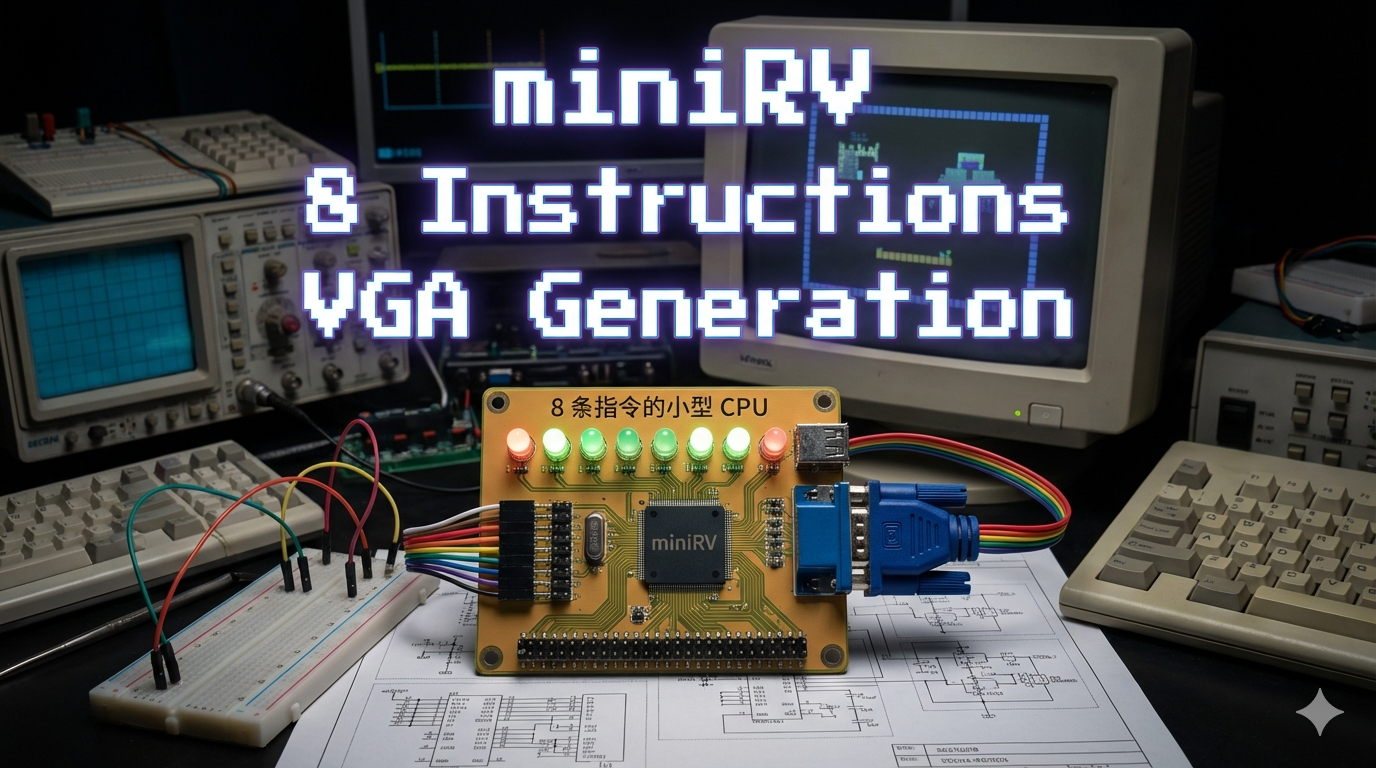

From miniRV to VGA image generation

A Trail of the project 一生一心

First meet with RISC-V, and first time to write a project blog

2026-03-03 开发日志:从 miniRV 到 VGA 图形验证

1. 工作简介

接触“一生一芯”项目的第一天,大致完成了F部分的任务目标:文档的要求是在Logisim上搭建出用8条指令实现rsc32基本功能的minirv。通过自己编写的mem/sum测试了add / addi / lui / lw / lbu / sw / sb / jalr8条指令的功能实现,确保功能没问题后跑通vga测试,生成“一生一芯”项目logo。

我的工作环境是MacOS。由于logisim电路搭建效率低,我决定直接基于icarus-verilog采用 iverilog + vvp 的方式将 rtl/minirv.v + tb/minirv_tb.v 编译成可执行仿真程序(build/simv / build/simv_vga),再进行vvp仿真,仿真结果通过check_output.c验证是否符合官方指导文档中的结果。

由于icarus-verilog无法直接解析官方v3.0 hex格式(该格式带有logisim识别用代码头),我通过logisim_hex_to_words.c将其转换为icarus-verilog可解析的word-hex格式。执行完vga测试后,通过fb_to_ppm.c将结果转换为可视化图片。

以上流程整理在Makefile中,CLI中 make test 执行,总耗时为4min。

2. 代码结构(目录与职责)

1 | RV32/ |

3. 知识点复盘

miniRV 指令集

ADD

1 | result = rs1_data + rs2_data |

ADDI

1 | result = rs1_data + imm |

LUI

1 | result = imm |

JALR(会修改 PC)

1 | result = rs1_data + imm |

SW

1 | addr = rs1_data + imm_s |

SB

1 | addr = rs1_data + imm_s |

LBU

1 | addr = rs1_data + imm_i |

LW

1 | addr = rs1_data + imm_i |

2 关于 icarus-verilog

icarus-verilog是轻量级的解释式 HDL 仿真器\- 对于大规模设计和复杂 testbench 速度不够快

可以使用同样开源的 Verilator:

Verilator 是一个开源的 Verilog/SystemVerilog 编译型模拟器

它将 Verilog 代码转换成高效的 C++/SystemC

模块,然后生成本地可执行程序

其仿真速度远快于解释式模拟器

MacOS 安装方式:

1 | brew install verilator |

4. Github

现有版本基本实现单周期minirv功能,项目已部署到https://github.com/Kingprotea787/RISC-V